## Enhancing Power Quality Making Use of a Multi-Level Inverter with Fewer Switching Devices and Lowest Standing Voltage.

T.Sreenivasa Murthy<sup>1</sup>, L.Venkateswarlu<sup>2</sup>, Ch.Kiran Kumar<sup>3</sup>, V.Pavan Kumar<sup>4</sup> Asst.Prof, EEE Department, QIS COLLEGE OF ENGINEERING AND TECHNOLOGY

#### **ABSTRACT**

Photovoltaic (PV) systems' power quality has been significantly improved by the widespread use of multilevel inverters (MLIs). However, the efficiency of a standard MLI is significantly impacted by the requirement for a large number of components, increased standing voltage, and high harmonic content in the output. Therefore, asymmetrical MLIs have been created as a good substitute to deal with these problems. The goal of the current study is to create a hybrid asymmetrical structure with a high level per component ratio and a low standing voltage that is appropriate for PV applications. An RSHB MLI structure with ansymmetrical repeating units and various level doubling circuit (LDC) combinations is used to assemble the suggested MLI. The suggested MLI structures, i.e., PS1 and PS2, may synthesis 4n+5 and 4n+7 levels, respectively, at the output instead of 2n+3 levels with merely RSHB MLI since the two dc sources employed in the repeating units have a voltage ratio of 1:n. According to a comparison, PS1 and PS2 both have fewer switches, a low standing voltage, reduced power loss, and are less expensive. For the purpose of evaluating the PS1 structure's performance, a 3.9 kW standalone solar PV system is taken into account. Both the selective harmonic elimination (SHE) and carrier-based pulse width modulation (PWM) control techniques are used. This justifies the LDC's self-voltage balancing mechanism and dc-link voltage balancing.

#### INTRODUCTION

Multilevel inverters (MLIs) have been evolved as an emerging power electronics converter in recent years. MLIs can produce high-quality output with lower switching frequency operation, thereby reducing the voltage stress, harmonic in the output, electromagnetic interference, switching loss, etc., compared to conventional two-level inverters in the process of electrical energy conversion. Due to their competency in solving the above issues, research focus has attracted MLI for numerous applications such as

electric drives, electric vehicles, railways, aircraft, and renewable energy systems. By the proper arrangement of dc-link, semiconductor switches, diodes, and capacitors, MLI produces a staircase output. MLIs are broadly classified into three categories, such as single dc-source flying capacitor MLI (FC MLI), single dc-source diode clamped MLI (DC MLI), multiple dc-sources cascaded H-bridge MLI (CHB MLI)

Regarding voltage balancing, design complexity, size, and cost [5], [10], the CHB MLI has a number of benefits. Because of this, CHB topology is mostly taken into account by researchers for progress and is suited for a variety of low voltage (230 V) to high voltage (>10 kV) level applications. The primary worry among researchers is the reduction in the number of semiconductor switches in MLI. In this regard, a number of MLI topologies that address the aforementioned problems have recently been designed. There has been an effort to lower the device counts. These topologies require approximately half as many switches as a typical CHB MLI does. However, higher voltage limits the switches' ability to operate due to increased voltage stress.

While this is going on, a few optimised MLI structures that were designed in can synthesise many levels at the output with fewer switches. These topologies, in contrast to the CHB MLI, can naturally produce negative levels. Voltage stress is a crucial factor that must be taken into consideration while planning the MLI for certain applications. In response to the aforementioned issue, the authors in have presented novel MLI topologies with a strategy to decrease both the voltage stress and the device count. A well-known method to produce many levels at the output is to use dc sources of the proper magnitude. Examples of this approach in use are topologies. For the purpose of determining the dc source magnitude, the authors have created a number of algorithms.

**Copyrights @Muk Publications**

Vol. 13 No.2 December, 2021

The choice of appropriate algorithms is a crucial element that will lead to the development of the highest levels feasible with little voltage stress on the switches. In addition to the widespread use and popularity of H-bridge based MLIs, one of the active research areas is the construction of various hybrid MLI structures. For instance, the MLI packed U cell compact module type MLI in [21] generates multilevel output without the need for an H-bridge. These modules/basic units can be cascaded in this situation to increase the number of tiers. On the other hand, the development of the level doubling circuit (LDC) has significantly advanced MLI technology.

LDCs integrated with MLI at different voltage magnitudes can be utilised to double the number of levels at the same active switch count. Recent years have seen the development of various pulse width modulation (PWM) methods as a primary concern for managing the voltage and current quality by producing the proper switching pulse for MLI. PWM control approaches are broadly divided into two classes, such as fundamental/low switching frequency control technique and high switching frequency control technique, depending on the operating frequency.

Techniques for high switching frequency control that use carrier-based PWM are highly effective in reducing THD levels and current waveform distortions. The only issue with these methods is increased switching loss. On the other hand, switching loss can be considerably decreased employing low switching frequency management approaches. One of the main switching control strategies that is frequently used to entirely attenuate the intended lower order harmonics is selective harmonic elimination (SHE). To find the best switching angles in this regard, a few rigorous mathematical calculations-based methodologies have been devised.

Additionally, popular stochastic techniques based on optimization algorithms like the genetic algorithm (GA), colonial competitive algorithm, cuckoo search algorithm (CSA), particle swarm optimization (PSO), etc., are examined critically with respect to equal and unequal dc sources. When MLIs are integrated with renewable sources, another method for optimal harmonic mitigation, i.e., to reduce each of the undesired harmonics along with calculation of appropriate switching angles, has been investigated. Further discussion thoroughly examines the suitability of photovoltaic (PV) system integration with the framework suggested in this work. In this situation, critical evaluation is required of concerns such as decreased power transfer level, MPPT failure, voltage balancing of dc-link, etc.

#### Literature survey

#### **Enhancing Power Quality of Modified Multilevel Inverter with Fewest Switches**

It Presents a modified nine level inverter design and execution for enhancing power quality with fewer switches. Here, we concentrate on two techniques: the modified inverter topology and the cascaded H Bridge

multilevel inverter topology. Both approaches make use of a pulse generator to create the proper switching pulses. When compared to a cascaded H-Bridge multilevel inverter, the improved topology's output quality is superior. When the levels are raised in the redesigned topology, fewer switches are needed than with a cascaded H bridge inverter. As a result, it lowers upfront costs and circuit complexity, making it suitable for industrial applications. The operation of the redesigned topology is described, and MATLAB/SIMULINK software is then used to assess the outcomes.

### An analysis of multilevel inverters with fewer Switches

Multilevel inverters have sparked a new wave of interest in business and research. While established topologies have become a viable option in a wide range of high-power, medium-voltage applications, there has been a strong drive for the development of newer topologies. A key goal of the recently described topologies has been to reduce overall part considerations in comparison to the traditional topologies. This research studies and evaluates a subset of the starting late proposed multilevel inverter topologies with fewer power switches. This essay will act as a companion and a redesign for these topologies, in terms of both arbitrary and objective criteria.

#### Topologies, Comprehensive Analysis, and Comparative Evaluation of a Recently Developed Reduced Switch Multilevel Inverter for Renewable Energy Integration and Drives Application

As they develop into a practical technology for many applications, including drives and systems for converting renewable energy, multilevel inverters (MLIs) have attracted a lot of attention from both industry and academics. One of the most cutting-edge power converter topologies, MLIs are frequently employed for these high power and high/medium voltage applications. Current research has focused heavily on the creation of reduced switch MLI (RS MLI) topologies, which can deliver high-quality output without the use of many switches. As a result, the focus of this review paper is on many recently created MLIs employed in various applications.

To assist with advanced current research in this field and in the selection of suitable inverter for various applications, significant understanding on these topologies is clearly summarized based on the three categories, i.e., symmetrical, asymmetrical, and modified topologies. This review paper also includes a comparison based on important performance parameters, detailed technical challenges, current focus, and future development trends. By a suitable combination of switches, the MLI produces a staircase output with low harmonic distortion. For a better understanding of the working principle, a single-phase RS MLI topology is experimentally illustrated for different level generation using both fundamental and high switching frequency techniques which will help

the readers to gain the utmost knowledge for advance research.

#### **Proposed Methodology**

#### **Diode Clamped multilevel inverter**

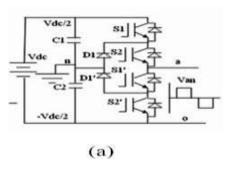

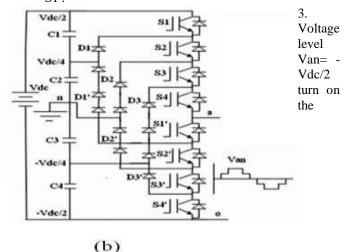

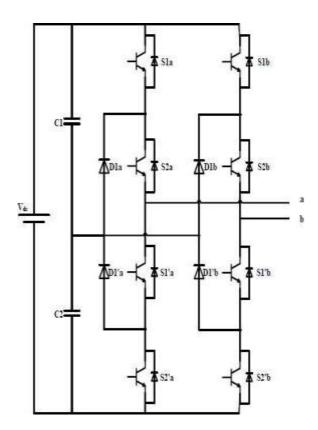

The diode clamped inverter, in which the diode is utilised as the clamping device to clamp the dc bus voltages so as to achieve steps in the output voltage, is the most widely used multilevel structure. The fundamental idea behind this inverter is to use diodes to reduce the voltage stress on the power devices. Each capacitor and switch is exposed to a voltage of Vdc. Two (n-1) switching devices, (n-1) (n-2) diodes, and (n-1) (n-1) voltage sources are required for a n level inverter. 5 level multilevel inverter with clamped diodes. Two pairs of switches and two diodes make up a three-level diode clamped inverter. Each switch pair operates in complementary mode, and access to the mid-point voltage is provided by the diodes. In inverters with three levels A commond cbus that has been subdivided into three levels by two capacitors is shared by all three of the inverter's phases. The DC capacitors C1 and C2 are connected in two series connections to divide the DC bus voltage into three voltage levels. voltage pressure

switchingdeviceislimitedtoVdcthroughtheclampingdio desDc1andDc2. Given that the midpoint is controlled at half of the DC link voltage and that the overall DC link voltage is Vdc, the voltage across each capacitor is Vdc/2 (Vc1=Vc2=Vdc/2). Three alternative switching modes that apply the stair case voltage on the output voltage in relation to the DC link capacitor voltage rate are conceivable in a three level diode clamped inverter. A set of two switches are always active in a three-level inverter, while four switches are always active in a five-level inverter.

A phase-leg a voltage and a phase-leg b voltage make up the line voltage Vab. For a three-level inverter, the resulting line voltage has a 5-level staircase waveform and a 9-level staircase waveform for a five-level inverter. So an N-level diode clamped inverter has a (2N-1) level output line voltage in addition to a N level output phase voltage. The voltage across each capacitor for an N-level diode clamped inverter is

typically Vdc/ (N-1). The clamping diodes need distinct ratings for reverse voltageblocking even if each active switching device is only required to block a voltage level of Vdc.

a three-level diode-clamped converter with two capacitors, C1 and C2, acting as the dc bus. The

voltage across each capacitor is Vdc/2, the fordc-bus voltage is Vdc, and the clamping diodes will limit the voltage stress on each device to one capacitor voltage level Vdc/2. Neutral point is taken into consideration as the output phase voltage reference point to illustrate how the staircase voltage is synthesised. To create three-level voltages across a and n, there are three switch combinations.

- 1.Voltage level Van= Vdc/2, turn on the switches S1 and S2.

- 2. Voltage level Van= 0, turn on the switches S2 and S1'.

switches S1',S2'.

a five-level diode-clamped converter with four capacitors (C1, C2, C3, and C4) making up the dc bus The voltage across each capacitor for dc-bus voltage Vdc is Vdc/4, and clamping diodes will limit each device's voltage stress to one capacitor voltage level of Vdc/4.

There are five switch combinations to synthesize five level voltages across a and n.

- 1) Voltage level Van= Vdc; turn on all upper switches S1, S2, S3 and S4.

- 2) Voltage level Van= Vdc/2, turn on the switches S2, S3, S4 and S1'.

- 3) Voltage level Van= 0, turn on the switches S3, S4, S1' and S2'.

- 4) Voltage level Van= -Vdc/2 turn on the switches S4, S1', S2',S3'.

- 5) Voltage level Van= -Vdc; turn on all lower switches S1', S2', S3' andS4'.

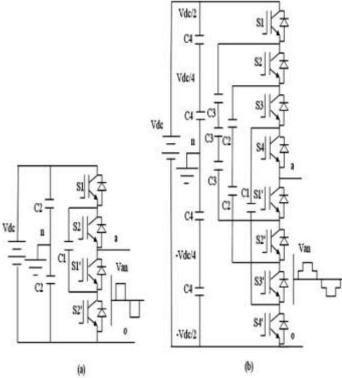

#### Flying Capacitor MultilevelInverter

This inverter's structure is comparable to that of a diode-clamped inverter, with the exception that capacitors are used in their place of clamping diodes. Switching cells with capacitor clamps are connected in series to create a flying capacitor. The voltage on each capacitor in this architecture is different from the voltage on the capacitor behind it, forming a ladder structure of dc side capacitors. The size of the voltage

steps in the output waveform is determined by the voltage increment between two adjacent capacitor legs. Fig 2.2 Capacitor-Clamped multilevel inverter

circuit topologies (a) 3-level inverter (b) 5-level inverter

#### **Operation of FCMLI**

Each phase node (a, b, or c) in the operating capacitor multi-level inverter can be connected to any node in the capacitor bank (V3, V2, V1). When S1 and S2 are turned on, the a-phase is connected to the positive node V3; when S2 and S1' are turned on, the a-phase is connected to the voltage at the neutral point. When both S1' and S2' are turned on, the negative node V1 is linked. When S1 and S1' are turned on, the clamped capacitor C1 is discharged. The same thing happens when S2 and S2' are turned on. Correct selection of the zero states can balance the capacitor's charge. In comparison to the three-level diode-clamped An additional switching state is achievable in an inverter. The level V3 is composed of two transistor states specifically. By choosing to charge or discharge the capacitor based on the direction of the a-phase flying capacitor current Ia for the redundant states, the capacitor voltage can be controlled to the desired value by switching within the phase. The highest and lowest switching states, similar to the three-level flying capacitor inverter, have no effect on how charged the capacitors are. Both capacitors can be controlled to their optimal voltages using the redundant states present at the two intermediate voltage levels.

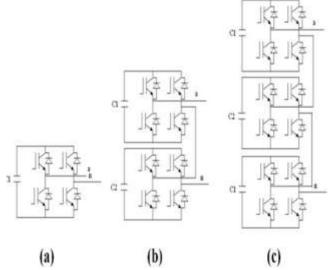

#### **Cascaded Multilevel Inverter**

The CMI creates its output by merging numerous separate voltage levels into approximately sinusoidal voltage waveforms. It is possible to achieve built-in redundancy against individual Hbridge converter failure by only increasing the number of H-bridge converters without redesigning the power stage. A phase for the inverter is made up of a string of single-phase complete bridges. A three-phase CMI architecture primarily consists of three identical phase legs of a series-chain of H-bridge converters, which has the ability to produce various output voltage waveforms and provides the possibility of AC system phase-balancing.

The series connection of single-phase inverters with independent dc sources is the foundation of the converter topology. the power circuit for one phase leg of a cascaded inverter with three, five, or seven levels. The voltages generated by the various cells are added to create the phase voltage that results. Each singlephase full-bridge inverter in a 3-level cascade inverter creates three voltages at the output: +Vdc, 0Vdc, and -Vdc (zero, positive dc voltage, and negative dc voltage). The power switches are used to successively connect the capacitors to the ac side in order to do this. The output ac voltage that results fluctuates between -Vdc and +Vdc with three levels, -2Vdc and +2Vdc with a five-level inverter, and 3Vdc and +3Vdc with a seven-level inverter. Even without filtering, the staircase waveform is essentially

Fig2.3 Single phase structures of Cascaded inverter (a) 3-level, (b) 5-level, (c) 7-level

#### Cascaded H - bridge multilevelinverter

The cascaded H-bride multi level inverter uses switches and capacitors and needs fewer components

per level. Power may be easily scaled with this design, which consists of a succession of power conversin cells. An H-bridge is a pair of

Fig2.4 Single phase structure of a cascaded H-bridge inverter

capacitors and switches that provides a distinct input DC voltage for each H-bridge. It is made up of H-bridge cells, each of which may supply one of three different voltages (zero, positive DC, and negative DC). When compared to diode clamped and flying capacitor inverters, this form of multi level inverter has the advantage of requiring fewer components. The inverter is less expensive and heavier than the other two inverters.

The idea behind this inverter is to provide a sinusoidal voltage output by series-connecting H-bridge inverters. The total voltage produced by all of the cells makes up the output voltage. There are 2n+1 levels of output voltage, where n is the number of cells. It is possible to select the switching angles to minimise total harmonic distortion. This type of multilevel inverter has the advantage of requiring less components than flying capacitor or diode clamped inverters, which lowers the cost and weight of the inverter in comparison to the two earlier types. This inverter uses the same method for calculating switching angles.

# **5 - level Cascaded H - bridge multilevel inverter**Similar to earlier multilevel inverters, this one provides a 5-level output voltage. This inverter is made

up of two cascaded H-bridge inverters. Eight switching devices are required for a cascaded H-bridge multilevel inverter with five levels. Multilevel inverter with 9 levels cascaded over a H bridge.

9 - level cascaded H - bridge multilevel inverter Similar to earlier multilevel inverters, the output voltage of this one has nine levels. This inverter is made up of four cascaded H-bridge inverters. There are 16 switching devices required for an H-bridge multilevel inverter with 9 levels.

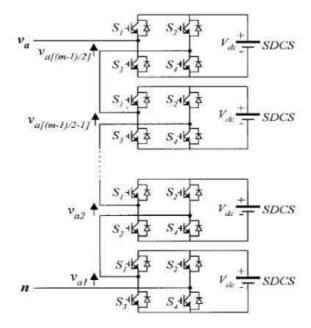

11 - level Cascaded H - bridge multilevel inverter A chain of H-bridge (single-phase full bridge) inverter units makes up a cascade multilevel inverter. Every Hbridge component has a separate dc source. Each single-phase full-bridge inverter is connected to a separate DC source (SDC). Different level inverters' ac terminal voltages are connected in series. a cascaded H-bridge inverter with distinct DC sources in a singlephase arrangement. Each converter level can produce one of three different voltage outputs-plus, minus, or zero—by combining the four switches, S1 through S4. Switches S1 and S4 are turned on to obtain +Vdcswitches. We receive the output-Vdc when S2 and S3 are turned on simultaneously. When the switches S1, S2, S3, and S4 are turned on simultaneously, we receive the output 0.

Different fullbridge converters' AC outputs are connected in series such that the synthesised voltage waveform is the sum of the outputs from each converter. The number of output-phase voltage levels in this architecture is determined by M=2N+1, where M is the number of levels and N is the number of DC sources. So, as an example, Van=Va1+Va2+Va3+Va4+Va5 gives the output phase voltage of an even level inverter.

## NEUTRAL POINT-CLAMPED MULTILEVEL INVERTER

Two series-connected capacitors, C1 and C2, make up the three-level Neutral Point-Clamped inverter. The DC-link capacitors divide the DC bus voltage into three levels. These voltage levels are produced at the inverter's output of each phase by the power semiconductor devices being switched in the proper manner. The neutral point, or "n," is the centre point of the two capacitors. In this inverter, each phase contains two clamping

Fig2.5 Neutral point-clamped multilevel inverter

diodes (D1, D1'), two complementary switch pairs (S1, S1'), and two complementary switch pairs (S2, S2'). While the inner two switches are the auxiliary switching devices (S2,S1') that clamp the output terminal potential to the neutral point potential with the aid of the two clamping diodes, the outer two switches are the primary switching devices (S1, S2') that function for pulse width modulation.

The voltage across "a" (the first phase) and "0" (the negative inverter terminal), commonly known as the pole voltage, is Vdc when both of the upper switches S1 and S2 are turned on. The voltage sharing between the two lower diodes is balanced by the lower clamping diode, D1'.

#### References

- [1] P. Kala and S. Arora, "A comprehensive study of classical and hybrid multilevel inverter topologies for renewable energy applications," *Renewable and Sustainable Energy Reviews*, vol. 76, pp. 905–931, Sep. 2017.

- [2] C. Cecati, F. Ciancetta, and P. Siano, "A Multilevel Inverter for Photovoltaic Systems WithFuzzy

- [3] F. Wu, X. Li, F. Feng, and H. B. Gooi, "Modified Cascaded Multilevel Grid-Connected Inverter to Enhance European Efficiency and Several Extended Topologies," *IEEE Transactions on Industrial Informatics*, vol. 11, no. 6, pp. 1358–1365, Dec. 2015.

S1' and S2' are switches. Similarly to how switch S1' blocks the voltage across C1, switch S2' does the same for C2. In contrast to the voltage between "a" and "n," which is an AC voltage, the voltage between "a" and "0" is a DC voltage. This is because the voltage across each capacitor is represented by the voltage appearing with respect to the negative inverter terminal ('0'), and the voltage appearing with respect to the inverter's neutral point ('n') is the sum of the capacitor voltages.

In order to obtain three levels across 'a'and'n', there are three switch combinations as follows:

- Turn on upper switches, S1 and S2, in order to obtain Van=+Vdc/2.

- Turn on middle switches, S2 and S1', in order to obtain Van =0.

- Turn on lower switches, S1' and S2', in order to obtain Van=-Vdc/2.

If we assume that each blocking diode has the same voltage rating as the active device and that each power device must block a voltage level of (Vdc/m-1) then the number of diodes needed for each phase will be (m-1) x (m-2). The relationship between the number of diodes and the level count of the multilayer inverter is quadratic.

#### Conclusion

In this paper, an asymmetrical DC source-based multilevel inverter is suggested. The proposal uses the fewest switches, and a voltage waveform with 17 levels is produced. The fundamental benefit of this inverter topology is that, in the asymmetric mode of operation, it only requires one DC supply and nine main switches to produce an output voltage with a 17-level distribution. When compared to earlier topologies, the overall THD (Total Harmonic Distortion) is relatively low, which improves the quality of the output waveform. The use of fewer switches allows for better circuit layout and packaging, which lowers the cost of building the suggested inverter. When comparing the two topologies, it is discovered that the proposed topology is more

- [4] J. Min, F. Ma, Q. Xu, Z. He, A. Luo, and A. Spina, "Analysis, Design, and Implementation of Passivity-Based Control for Multilevel Railway Power Conditioner," *IEEE Transactions on Industrial Informatics*, vol. 14, no. 2, pp. 415–425, Feb.2018.

- [5] S. K. Chattopadhyay and C. Chakraborty, "A New Asymmetric Multilevel Inverter Topology Suitable for Solar PV Applications With Varying Irradiance," *IEEE Transactions* 90th Sastainable Effects, Transactions of 1496–1506, Oct. 2017.

- [6] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4,pp. 724–738, Aug. 2002.

800

- [7] K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel Inverter Topologies With Reduced Device Count: A Review," *IEEE Transactions on Power Electronics*, vol. 31, no. 1, pp. 135–151, Jan.2016.

- [8] H. R. Massrur, T. Niknam, M. Mardaneh, and A. H. Rajaei, "Harmonic Elimination in Multilevel Inverters Under Unbalanced Voltages and Switching Deviation Using a New Stochastic Strategy," *IEEE Transactions on Industrial Informatics*, vol. 12, no. 2, pp. 716–725, Apr.2016.

- [9] M. Sharifzadeh, H. Vahedi, A. Sheikholeslami, P. Labbé, and K. Al- Haddad, "Hybrid SHM-SHE Modulation Technique for a Four-Leg NPC Inverter WithDC Capacitor Self- Voltage Balancing," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 8, pp. 4890–4899, Aug. 2015.

- [10] K. Haghdar and H. A. Shayanfar, "Selective Harmonic Elimination With Optimal DC Sources in Multilevel Inverters Using Generalized Pattern Search," *IEEE Transactions on Industrial Informatics*, vol. 14, no. 7, pp. 3124–3131, Jul.2018.

- [11] T. Atalik*et al.*, "Multi-DSP and -FPGA-Based Fully Digital Control System for Cascaded Multilevel Converters Used in FACTS Applications," *IEEE Transactions on Industrial Informatics*, vol. 8, no. 3, pp. 511–527, Aug.2012.

- [12] S. S. Lee, M. Sidorov, C. S. Lim, N. R. N. Idris, and Y. E. Heng, "Hybrid Cascaded Multilevel Inverter (HCMLI) With Improved Symmetrical 4-Level Submodule," *IEEE Transactions on Power Electronics*, vol. 33, no. 2, pp. 932–935, Feb.2018.

- [13] R. S. Alishah, S. H. Hosseini, E. Babaei, and M. Sabahi, "Optimal Design of New Cascaded Switch-Ladder Multilevel Inverter Structure," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 3, pp. 2072–2080, Mar.2017.

- [14] A. Hota, S. Jain, and V. Agarwal, "An Optimized Three-Phase Multilevel Inverter Topology With Separate Level and Phase Sequence Generation Part," *IEEE Transactions on Power Electronics*, vol. 32, no. 10, pp. 7414–7418, Oct.2017.

- [15] E. Samadaei, A. Sheikholeslami, S. A. Gholamian, and J. Adabi, "A Square T-Type (ST- Type) Module for Asymmetrical Multilevel Inverters," *IEEE Transactions on Power Electronics*, vol. 33, no. 2, pp. 987–996, Feb.2018

- [16] Tabassum, Saleha, and B. Mouli Chandra.

"Power Quality improvement by UPQC using ANN Controller." International Journal of Engineering Research and Applications 2.4 (2012): 2019-2024.

- [17] Chandra, B. Mouli, and Dr S. Tara Kalyani.

"FPGA controlled stator resistance estimation in IVC of IM using FLC." Global Journal of Researches in Engineering Electrical and Electronics Engineering 13.13 (2013).

- [18] Chandra, B. Mouli, and S. Tara Kalyani. "Online identification and adaptation of rotor resistance in feedforward vector controlled induction

- motor drive." Power Electronics (IICPE), 2012 IEEE 5th India International Conference on. IEEE, 2012.

- [19] Chandra, B. Mouli, and S. Tara Kalyani. "Online estimation of Stator resistance in vector control of Induction motor drive." Power India Conference, 2012 IEEE Fifth. IEEE, 2012.

- [20] MURALI, S., and B. MOULI CHANDRA.

"THREE PHASE 11-LEVEL INVERTER WITH

REDUCED NUMBER OF SWITCHES FOR GRID

CONNECTED PV SYSTEMS USING VARIOUS

PWM TECHNIQUES."

- [21] BABU, GANDI SUNIL, and B. MOULI CHANDRA. "POWER QUALITY IMPROVEMENT WITH NINE LEVEL MULTILEVEL INVERTER FOR SINGLE PHASE GRID CONNECTED SYSTEM."

- [22] NAVEENKUMAR, K., and B. MOULI CHANDRA. "Performance Evaluation of HVDC Transmission system with the Combination of VSC and H-Bridge cells." Performance Evaluation 3.02 (2016).

- [23] Vijayalakshmi, R., G. Naga Mahesh, and B. Mouli Chandra. "Seven Level Shunt Active Power Filter for Induction Motor Drive System." International Journal of Research 2.12 (2015): 578-583.

- [24] BAI, RM DEEPTHI, and B. MOULI CHANDRA. "Speed Sensorless Control Scheme of Induction Motor against Rotor Resistance Variation." (2013).

- [25] Chandra, B. Mouli, and S. Tara Kalyani.

"Online Rotor Time Constant Tuning in Indirect

Vector Control of Induction Motor

Drive." International Journal on Engineering

Applications (IREA) 1.1 (2013): 10-15.

- [26] Rajesh, P., Shajin, F. H., Mouli Chandra, B., & Kommula, B. N. (2021). Diminishing Energy Consumption Cost and Optimal Energy Management of Photovoltaic Aided Electric Vehicle (PV-EV) By GFO-VITG Approach. Energy Sources, Part A: Recovery, Utilization, and Environmental Effects, 1-19.

- [27] Reddy C, Narukullapati BK, Uma Maheswara Rao M, Ravindra S, Venkatesh PM, Kumar A, Ch T, Chandra BM, Berhanu AA. Nonisolated DC to DC Converters for High-Voltage Gain Applications Using the MPPT Approach. Mathematical Problems in Engineering. 2022 Aug 22;2022.

- [28] Sravani, B., C. Moulika, and M. Prudhvi.

"Touchless door bell for post-covid." South Asian

Journal of Engineering and Technology 12.2 (2022):

54-56.

- [29] Mounika, P., V. Rani, and P. Sushma. "Embedded solar tracking system using arduino." South Asian Journal of Engineering and

- Technology 12.2 (2022): 1-4.

- [30] Prakash, A., Srikanth, T., Moulichandra, B., & Krishnakumar, R. (2022, February). Search and Rescue Optimization to solve Economic Emission Dispatch. In 2022 First International Conference on Electrical, Electronics, Information and Communication Technologies (ICEEICT) (pp. 1-5). IEEE.

- [31] Kannan, A. S., Srikanth Thummala, and B. Mouli Chandra. "Cost Optimization Of Micro-Grid Of Renewable Energy Resources Connected With And Without Utility Grid." Materials Today: Proceedings (2021).

- [32] Chandra, B. M., Sonia, D., Roopa Devi, A., Yamini Saraswathi, C., Mighty Rathan, K., & Bharghavi, K. (2021). Recognition of vehicle number plate using Matlab. J. Univ. Shanghai Sci. Technol, 23(2), 363-370.

- [33] Dr. M. Thangamani, Jafar Ali Ibrahim, Information Technology E-Service Management System, International Scientific Global Journal in Engineering Science and Applied Research (ISGJESAR). Vol.1. Issue 4, pp. 13-18, 2017. http://isgjesar.com/Papers/Volume1,Issue4/paper2.pdf

- [34] Ibrahim, Mr S. Jafar Ali, K. Singaraj, P. Jebaroopan, and S. A. Sheikfareed. "Android Based Robot for Industrial Application." International Journal of Engineering Research & Technology 3, no. 3 (2014).

- [35] Ibrahim, S. Jafar Ali, and M. Thangamani.

"Momentous Innovations in the Prospective Method of

Drug Development." In Proceedings of the 2018

International Conference on Digital Medicine and

Image Processing, pp. 37-41. 2018.

- [36] Ibrahim, S. Jafar Ali, and M. Thangamani.

"Prediction of Novel Drugs and Diseases for Hepatocellular Carcinoma Based on Multi-Source Simulated Annealing Based Random Walk." Journal of medical systems 42, no. 10 (2018): 188. https://doi.org/10.1007/s10916-018-1038-yISSN 1311-8080, https://acadpubl.eu/hub/2018-119-16/1/94.pdf

- [37] Jafar Ali Ibrahim. S, Mohamed Affir. A "Effective Scheduling of Jobs Using Reallocation of Resources Along With Best Fit Strategy and Priority", International Journal of Science Engineering and Advanced Technology(IJSEAT) ISSN No: 2321-6905, Vol.2, Issue.2, Feb-2014, <a href="http://www.ijseat.com/index.php/ijseat/article/view/62">http://www.ijseat.com/index.php/ijseat/article/view/62</a>

- [38] M. Thangamani, and Jafar Ali Ibrahim. S,

"Knowledge Exploration in Image Text Data using

Data Hiding Scheme," Lecture Notes in Engineering

and Computer Science: Proceedings of The

International MultiConference of Engineers and

Computer Scientists 2018, 14-16 March, 2018, Hong

Kong,

pp352357<a href="http://www.iaeng.org/publication/IMECS2018/IMECS2018">http://www.iaeng.org/publication/IMECS2018/IMECS2018</a> pp352-357.pdf

- [39] M. Thangamani, and Jafar Ali Ibrahim. S, "Knowledge Exploration in Image Text Data using Data Hiding Scheme," Lecture Notes in Engineering

- and Computer Science: Proceedings of The International MultiConference of Engineers and Computer Scientists 2018, 14-16 March, 2018, Hong Kong, pp352-357<a href="http://www.iaeng.org/publication/IMECS2018/IMECS2018">http://www.iaeng.org/publication/IMECS2018/IMECS2018</a> pp352-357.pdf

- [40] S. Jafar Ali Ibrahim and M. Thangamani. 2018. Momentous Innovations in the Prospective Method of Drug Development. In Proceedings of the 2018 International Conference on Digital Medicine and Image Processing (DMIP '18). Association for Computing Machinery, New York, NY, USA, 37–41. https://doi.org/10.1145/3299852.3299854

- [41] S. Jafar Ali Ibrahim and Thangamani, M "Proliferators and Inhibitors Of Hepatocellular Carcinoma", International Journal of Pure and Applied Mathematics (IJPAM) Special Issue of Mathematical Modelling of Engineering ProblemsVol 119 Issue. 15. July 2018

- [42] Thangamani, M., and S. Jafar Ali Ibrahim.

"Ensemble Based Fuzzy with Particle Swarm Optimization Based Weighted Clustering (Efpso-Wc) and Gene Ontology for Microarray Gene Expression."In Proceedings of the 2018 International Conference on Digital Medicine and Image Processing, pp. 48-55. 2018.

https://dl.acm.org/doi/abs/10.1145/3299852.3299866

- [43] Dr.R.Chinnaiyan, Abishek Kumar (2017) " Reliability Assessment of Component Based Software Systems using Basis Path Testing", IEEE International Conference on Intelligent Computing and Control Systems, ICICCS 2017, 512 – 517

- [44] Dr.R.Chinnaiyan, AbishekKumar(2017) ,"Construction of Estimated Level Based Balanced Binary Search Tree", 2017 IEEE International Conference on Electronics, Communication, and Aerospace Technology (ICECA 2017), 344 - 348, 978-1-5090-5686-6.

- [45] R.Chinnaiyan, S.Somasundaram (2012), Reliability Estimation Model for Software Components using CEP", International Journal of Mechanical and Industrial Engineering (IJMIE), ISSN No.2231-6477, Volume-2, Issue-2, 2012, pp.89-93.

- [46] R.Chinnaiyan, S. Somasundaram (2011) ,"An SMS based Failure Maintenance and Reliability Management of Component Based Software Systems", European Journal of Scientific Research, Vol. 59 Issue 1, 9/1/2011, pp.123 (cited in EBSCO, Impact Factor: 0.045)

- [47] R.Chinnaiyan, S.Somasundaram(2011), "An Experimental Study on Reliability Estimation of GNU Compiler Components A Review", International Journal of Computer Applications, Vol.25, No.3, July 2011, pp.13-16. (Impact Factor: 0.814)

- [48] R.Chinnaiyan, S.Somasundaram(2010) "Evaluating the Reliability of Component Based Software Systems", International Journal of Quality and Reliability Management, Vol. 27, No. 1., pp. 78-88 (Impact Factor: 0.406)

- [49] Dr.R.Chinnaiyan, AbishekKumar(2017), Estimation of Optimal Path in Wireless Sensor

- Networks based on Adjancy List, 2017 IEEE International Conference on Telecommunication, Power Analysis and Computing Techniques (ICTPACT2017), 6,7,8th April 2017, IEEE 978-1-5090-3381-2.

- [50] Ibrahim, S. Jafar Ali, and M. Thangamani. "Enhanced singular value decomposition for prediction of drugs and diseases with hepatocellular carcinoma based on multi-source bat algorithm based random walk." Measurement 141 (2019): 176-183. https://doi.org/10.1016/j.measurement.2019.02.056

- [51] Compound feature generation and boosting model for cancer gene classification Ibrahim, S. Jafar Ali Ibrahim., Affir, A.M., Thangamani, M.International Journal of Engineering Trends and Technology, 2020, 68(10), pp. 48–51, Doi No:doi:10.14445/22315381/IJETT-V68I10P208 https://ijettjournal.org/Volume-68/Issue-10/IJETT-V68I10P208.pdf

- [52] Innovative drug and disease prediction with dimensionality reduction and intelligence based random walk methods, Ibrahim, S.J.A., Thangamani, M.International Journal of Advanced Trends in Computer Science and Engineering, 2019, 8(4), pp. 1668–1673, <a href="https://www.warse.org/IJATCSE/static/pdf/file/ijatcse9">https://www.warse.org/IJATCSE/static/pdf/file/ijatcse9</a> 3842019.pdf

- [53] R. Ganesan, M. Thangamani, S. Jafar Ali Ibrahim, "Recent Research Trends and Advancements in Computational Linguistics", International Journal of Psychosocial Rehabilitation Vol 24, no 8 (2020):1154-1162, DOI: 10.37200/IJPR/V24I8/PR280128

- [54] C. Narmatha, Dr. M. Thangamani, S. Jafar Ali Ibrahim, "Research Scenario of Medical Data Mining Using Fuzzy and Graph theory", International Journal of Advanced Trends in Computer Science and Engineering, Vol 9, No 1 (2020): 349-355

- [55] Dr.R.Chinnaiyan, R.Divya (2018), "Reliable AIBasedSmartSensorsforManagingIrrigationResources in Agriculture", Lecture Notes on DataEngineeringandCommunicationsTechnologies,Spri ngerInternationalconferenceonComputerNetworksandIn ventiveCommunicationTechnologies(ICCNCT-2018),August2018

- [56] Dr.R.Chinnaiyan, S.Balachandar (2018), "Reliab le Digital Twin for Connected Footballer" ,LectureNotesonDataEngineeringandCommunicationsT echnologies, SpringerInternationalconferenceonComput erNetworksandInventiveCommunicationTechnologies (I CCNCT-2018), August 2018

- [57] Dr.R.Chinnaiyan,S.Balachandar(2018), "Centra lized Reliability and Security Management ofDatainInternetofThings(IoT)withRuleBuilder"Lectur eNotesonDataEngineeringandCommunicationsTechnol ogies,SpringerInternationalconferenceonComputerNet worksandInventiveCommunicationTechnologies(ICCN CT- 2018),August 2018(Online)

- [58] Dr.R.Chinnaiyan,AbishekKumar(2017)"Reliab ilityAssessmentofComponentBasedSoftware Systems

- using Basis Path Testing", IEEEInternational Conference on Intelligent Computingand ControlSystems, ICICCS2017, 512–517

- [59] Dr.R.Chinnaiyan,

AbishekKumar(2017,"Construction of Estimated Level

Based

BalancedBinarySearchTree",2017IEEEInternationalCo

nferenceonElectronics,Communication,andAerospaceT

echnology(ICECA2017),344 -348,978-1-5090-5686-6.

- [60] Dr.R.Chinnaiyan, AbishekKumar(2017),

Estimationof Optimal Path in Wireless Sensor

Networks

basedonAdjancyList,2017IEEEInternationalConference

on Telecommunication,Power Analysisand

Computing Techniques (ICTPACT2017)

,6,7,8thApril2017,IEEE978-1-5090-3381-2.

- [61] Dr.R.Chinnaiyan,R.Divya(2017),"ReliabilityE valuationofWirelessSensorNetworks",IEEEInternationa l Conference on Intelligent Computingand ControlSystems, ICICCS2017, 847–852

- [62] Dr.R.Chinnaiyan,Sabarmathi.G(2017),"Investi gationsonBigDataFeatures,ResearchChallengesandAppl ications",IEEEInternational Conference on Intelligent Computing and ControlSystems,ICICCS 2017, 782– 786

- [63] G.Sabarmathi, Dr.R. Chinnaiyan (2018), "Envisa gationand Analysis of Mosquito Borne Fevers A Health Monitoring System by Envisagative Computing using Big Data Analytics" in ICC BI 2018 Springer on 19.12.2018 to 20.12.2018 (Recommended for Scopus Indexed Publication IEEEX plored igital library)

- [64] G.Sabarmathi, Dr.R. Chinnaiyan, Reliable Data Mining Tasks and Techniques for Industrial Applications, IA ETSD JOURNAL FOR ADVANCE DRESEARCHINAP PLIED SCIENCES, VOLUME 4, ISSUE 7, DEC/2017, PP-138-142, ISSN NO: 2394-8442